#### **Key Specifications\* and Characteristics**

| 16715A, 16716A: 167 Mb/s<br>16717A, 333 Mb/s [1]                                                                       | 200 Mb/s                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 400 NAL /- [1]                                                                                                         |                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 400 Mb/s [1]                                                                                                           | Full channel: 800 Mb/s<br>Half channel: 1.5 Gb/s                                                                                                                                                                      |

| Timing Zoom: 2 GHz (16716A,<br>16717A only)<br>Conventional: 667/333 MHz<br>Transitional: 333 MHz                      | Timing Zoom: 2 GHz<br>Conventional: 800/400 MHz<br>Transitional: 400 MHz                                                                                                                                                                                                                                                                                                                                                                                                          | Timing Zoom: 2 GHz<br>Conventional: 800/400 MHz<br>Transitional: 400 MHz                                               | Conventional: 800 MHz<br>Transitional: 400 MHz                                                                                                                                                                        |

| 68                                                                                                                     | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68                                                                                                                     | 34                                                                                                                                                                                                                    |

| 340 (5 modules)                                                                                                        | 340 (5 modules)                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 340 (5 modules)                                                                                                        | 170 (5 modules)                                                                                                                                                                                                       |

| 16715A, 16717A: 4/2M [2]<br>16716A: 1M/512K [2]                                                                        | 16740A: 2/1 M [2]<br>16741A: 8/4 M [2]<br>16742A 32/16 M [2]                                                                                                                                                                                                                                                                                                                                                                                                                      | 16750B: 8/4M [2]<br>16751B: 32/16M [2]<br>16752B: 64/32M [2]                                                           | 128/64M [5]                                                                                                                                                                                                           |

| Patterns: 16 Ranges: 15 Edge & Glitch: 2 Timers: (2 per module) -1 Occurrence Counter: [4] Global Counters: 2 Flags: 4 | Pattern: 16 Ranges: 15 Edge & Glitch: 2 Timers: (2 per module) -1 Occurrence Counter: 2 Global Counter: 2 Flags: 4                                                                                                                                                                                                                                                                                                                                                                | Patterns: 16 Ranges: 15 Edge & Glitch: 2 Timers: (2 per module) -1 Occurrence Counter: [4] Global Counters: 2 Flags: 4 | At 800 Mb/s: 4 patterns or<br>2 ranges, 4 flags, arm in<br>At 200 Mb/s: same as<br>16750B/51B/52B<br>Other speeds: refer to<br>synchronous state analysis<br>(page 97) and asynchronous<br>timing analysis (page 100) |

| 16                                                                                                                     | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16                                                                                                                     | 1.5 Gb/s: 2<br>800 Mb/s: 4<br>200 or 400 Mb/s: 16                                                                                                                                                                     |

| 16715A, 16716A: 167 MHz<br>16717A: 333 MHz                                                                             | 200 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 400 MHz                                                                                                                | 1.5 GHz                                                                                                                                                                                                               |

| 4-way arbitrary "IF/THEN/ELSE"<br>branching                                                                            | 4-way arbitrary<br>"IF/THEN/ELSE"<br>branching                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-way arbitrary "IF/THEN/ELSE"<br>branching                                                                            | 800 or 1.5 Gb/s: none<br>200 Mb/s: arbitrary<br>"IF/THEN/ELSE" branching<br>400 Mb/s: dedicated next-<br>state branch or reset                                                                                        |

| 4                                                                                                                      | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                                                                                                                      | 1 (state clock only)                                                                                                                                                                                                  |

| 2.5 ns window adjustable from<br>4.5/-2.0 ns to -2.0/4.5 ns in 100 ps<br>increments per channel [3]                    | 2.5 ns windows adjustable from<br>4.5/2.0 ns to -2.0/4.5 ns in 100 ps<br>increments per channel [3]                                                                                                                                                                                                                                                                                                                                                                               | 2.5 ns window adjustable from<br>4.5/-2.0 ns to -2.0/4.5 ns in 100 ps<br>increments per channel [3]                    | 1 ns window adjustable from<br>2.5/-1.5 ns to -1.5/2.5 ns<br>10 ps increments per channel                                                                                                                             |

| TTL, ECL, user-definable ±6.0 V adjustable in 10-mV increments                                                         | TTL, ECL, user-definable ±6.0 V adjustable in 10-mV increments                                                                                                                                                                                                                                                                                                                                                                                                                    | TTL, ECL, user-definable ±6.0 V adjustable in 10-mV increments                                                         | -3.0 V to 5.0 V adjustable in 10-mV increments                                                                                                                                                                        |

|                                                                                                                        | 16717A only) Conventional: 667/333 MHz Transitional: 333 MHz  68  340 (5 modules)  16715A, 16717A: 4/2M [2] 16716A: 1M/512K [2]  Patterns: 16 Ranges: 15 Edge & Glitch: 2 Timers: (2 per module) -1 Occurrence Counter: [4] Global Counters: 2 Flags: 4  16  16715A, 16716A: 167 MHz 16717A: 333 MHz  4-way arbitrary "IF/THEN/ELSE" branching  4  2.5 ns window adjustable from 4.5/-2.0 ns to -2.0/4.5 ns in 100 ps increments per channel [3]  TTL, ECL, user-definable ±6.0 V | 16717A only    Conventional: 800/400 MHz                                                                               | 16717A only                                                                                                                                                                                                           |

<sup>\*</sup> All specifications noted by an asterisk are the performance standards against which the product is tested.

[1] State speeds greater than 167 MHz (16717A) or 200 MHz (16750B, 16751B, 16752B, 16760A) require a trade-off in features. Refer to "Supplemental Specifications and Characteristics" on page 93 for more information.

<sup>[2]</sup> Memory depth doubles in half-channel timing mode only.

<sup>[3]</sup> Minimum setup/hold time specified for a single clock, single edge acquisition. Multi-clock, multi-edge setup/hold window add 0.5 ns.

<sup>[4]</sup> There is one occurrence counter per trigger sequence level.

<sup>[5]</sup> Memory depth doubles in half-channel 1.25 Gb/s and 1.5 Gb/s modes only.

#### **Key Specifications\* and Characteristics (continued)**

| Agilent Model Number                                    | 16710A, 16711A, 16712A                                                                            | 16753A, 16754A, 16755A, 16756A                                                                                         |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Maximum state acquisition rate on each channel          | 100 Mb/s                                                                                          | 600 Mb/s                                                                                                               |

| Maximum timing sample rate (half/full channel)          | Conventional: 500/250 MHz<br>Transitional: 125 MHz                                                | Timing Zoom: 4 GHz<br>Conventional: 1200/600 MHz<br>Transitional: 600 MHz                                              |

| Channels/module                                         | 102                                                                                               | 68                                                                                                                     |

| Maximum channel count on a single time base and trigger | 204 (2 modules)                                                                                   | 340 (5 modules)                                                                                                        |

| Memory depth (half/full channel)                        | 16710A: 16/8K[1]<br>16711A: 64/32K[1]<br>16712A: 256/128k[1]                                      | 16753A: 2/1M [1]<br>16754A: 8/4M [1]<br>16755A: 32/16M [1]<br>16756A: 128/64M [1]                                      |

| Trigger resources                                       | Patterns: 10<br>Ranges: 2<br>Edge & Glitch: 2<br>Timers: 2                                        | Patterns: 16 Ranges: 15 Edge & Glitch: 2 Timers: (2 per module) -1 Occurrence Counter: [3] Global Counters: 2 Flags: 4 |

| Maximum trigger sequence levels                         | State mode: 12<br>Timing mode: 10                                                                 | Patterns: 16 Ranges: 15 Edge & Glitch: 2 Timers: (2 per module) -1 Occurrence Counter: [3] Global Counters: 2 Flags: 4 |

| Maximum trigger sequence speed                          | 125 MHz                                                                                           | 600 MHz                                                                                                                |

| Trigger sequence level branching                        | Dedicated next state or single arbitrary branching                                                | 4-way arbitrary "IF/THEN/ELSE" branching                                                                               |

| Number of state clocks/qualifiers                       | 6                                                                                                 | 4                                                                                                                      |

| Setup/hold time*                                        | 4.0 ns window adjustable from<br>4.0/0 ns to 0/4.0 ns in 500 ps<br>increments [2] per 34 channels | 1 ns window (600ps typical) adjustable in 80ps increments                                                              |

| Threshold range                                         | TTL, ECL, user-definable ±6.0 V adjustable in 50 mV increments                                    | -3.0 V to +5.0 V adjustable in<br>10-mV increments                                                                     |

<sup>\*</sup> All specifications noted by an asterisk are the performance standards against which the product is tested.

<sup>[1]</sup> Memory depth doubles in half-channel timing mode only.

<sup>[2]</sup> Minimum setup/hold time specified for single-clock, single-edge acquisition. Single-clock, multi-edge setup/hold add 0.5 ns. Multi-clock, multi-edge setup/hold window add 1.0 ns.

<sup>[3]</sup> There is one occurrence counter per trigger sequence level.

#### Agilent Technologies 16710A, 16711A, 16712A Supplemental Specifications\* and Characteristics

#### Probes (general-purpose lead set)

| Input resistance          | 100 KΩ, ±2%                              |

|---------------------------|------------------------------------------|

| Parasitic tip capacitance | 1.5 pF                                   |

| Minimum voltage swing     | 500 mV, peak-to-peak                     |

| Threshold accuracy*       | $\pm$ (100 mV + 3% of threshold setting) |

| Maximum input voltage     | ±40 V peak                               |

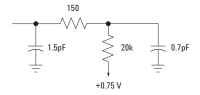

# 370 ohms 1.5pF 7.4pF 100K ohm GROUND

Figure 6.9. Equivalent probe load for the Agilent 16710A, 16711A and 16712A, generalpurpose lead set.

#### State Analysis

| Minimum state clock pulse width                  | 3.5 ns                        |

|--------------------------------------------------|-------------------------------|

| Time tag resolution [1]                          | 8 ns                          |

| Maximum time count between states                | 34 seconds                    |

| Maximum state tag count between states [1]       | 4.29 x 10 <sup>9</sup> states |

| Minimum master to master clock time*             | 16710A, 16711A, 16712A: 10 ns |

| Minimum master to slave clock time               | 0.0 ns                        |

| Minimum slave to master clock time               | 4.0 ns                        |

| Context store block sizes<br>16710A/11A/12A only | 16, 32, 64 states             |

#### **Timing Analysis**

| Sample period accuracy    | 0.01% of sample period                                                          |  |

|---------------------------|---------------------------------------------------------------------------------|--|

| Channel-to-channel skew   | 2 ns, typical                                                                   |  |

| Time interval accuracy    | ± (sample period + channel-to-channel<br>skew + 0.01% of time interval reading) |  |

| Minimum detectable glitch | 3.5 ns                                                                          |  |

<sup>\*</sup> All specifications noted by an asterisk are the performance standards against which the product is tested.

<sup>[1]</sup> Time or state tags halve the acquisition memory when there are no unassigned pods.

## Agilent Technologies 16710A, 16711A, 16712A Supplemental Specifications\* and Characteristics (continued)

#### Triggering

| Maximum trigger sequence speed | 125 MHz, maximum                                                                                                                      |  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Maximum occurrence counter     | 1,048,575                                                                                                                             |  |

| Range width                    | 32 bits each                                                                                                                          |  |

| Timer value range              | 400 ns to 500 seconds                                                                                                                 |  |

| Timer resolution               | 16 ns or 0.1% whichever is greater                                                                                                    |  |

| Timer accuracy                 | ±32 ns or ±0.1% whichever is greater                                                                                                  |  |

| Operating Environment          |                                                                                                                                       |  |

| Temperature                    | Agilent 16700 Series mainframes: • Instrument 0°C to 50°C (+32°F to 122°F) • Probe lead sets and cables, 0°C to 65°C (+32°F to 149°F) |  |

| Humidity                       | 80% relative humidity at +40°C                                                                                                        |  |

| Altitude                       | Operating 4600m (15,000ft)<br>Nonoperating 15,300m (50,000ft)                                                                         |  |

<sup>\*</sup> All specifications noted by an asterisk are the performance standards against which the product is tested.

# Agilent Technologies 16715A, 16716A, 16717A, 16740A, 16741A, 16742A, 16750B, 16751B, 16752B Supplemental Specifications\* and Characteristics

#### Probes (general-purpose lead set)

| Input resistance          | 100 ΚΩ, ± 2%                                                                                |  |

|---------------------------|---------------------------------------------------------------------------------------------|--|

| Parasitic tip capacitance | 1.5 pF                                                                                      |  |

| Minimum voltage swing     | 500 mV, peak-to-peak                                                                        |  |

| Minimum input overdrive   | 250 mV                                                                                      |  |

| Threshold range           | -6V to +6V in 10 mV increments                                                              |  |

| Threshold accuracy*       | ± (65 mV + 1.5% of settings)                                                                |  |

| Input dynamic range       | ± 10V about threshold                                                                       |  |

| Maximum input voltage     | ± 40V peak                                                                                  |  |

| +5V Accessory current     | 1/3 amp maximum per pod                                                                     |  |

| Channel assignment        | Each group of 34 channels can be assigned to<br>Analyzer 1, Analyzer 2 or remain unassigned |  |

# 370 ohms 1.5pF 7.4pF 100K ohm GROUND

Figure 6.10. Equivalent probe load for the Agilent 16715A, 16716A, 16717A, 16718A, 16719A, 16750B, 16751B, 16752B generalpurpose lead set.

#### 2 GHz Timing Zoom (Agilent 16716A, 16717A, 16740A, 16741A, 16742A, 16750B, 16751B, 16752B only)

| 2 GHz/1 GHz/500 MHz/250 MHz                                                  |  |

|------------------------------------------------------------------------------|--|

| ± 50 ps                                                                      |  |

| < 1.0 ns                                                                     |  |

| ± (sample period + channel-to-channel skew + 0.01% of time interval reading) |  |

| 16 K                                                                         |  |

| Start, center, end, or user defined                                          |  |

|                                                                              |  |

#### **Operating Environment**

| Temperature | Agilent 16700 Series frame: 0°C to 50°C (+32°F to 122°F)<br>Probe lead sets and cables: 0°C to 65°C (+32°F to 149°F) |  |

|-------------|----------------------------------------------------------------------------------------------------------------------|--|

| Humidity    | 80% relative humidity at + 40°C                                                                                      |  |

| Altitude    | Operating 4600 m (15,000 ft)<br>Non-operating 15,300 m (50,000 ft)                                                   |  |

<sup>\*</sup> All specifications noted by an asterisk are the performance standards against which the product is tested.

#### Agilent Technologies 16715A, 16716A, 16717A, 16740A, 16741A, 16742A, 16750B, 16751B, 16752B Supplemental Specifications\* and Characteristics

| State Mode                                                         | 16715A, 16716A, 16717A<br>167 Mb/s State Mode                                             | 16740A, 16741A, 16742A<br>16750B, 16751B, 16752B<br>200 Mb/s State Mode                   |  |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| Maximum state acquisition rate on each channel                     | 167 Mb/s                                                                                  | 200 Mb/s                                                                                  |  |

| Channel count                                                      | 68 per module                                                                             | 68 per module                                                                             |  |

| Maximum channels on a single time base and trigger                 | 340                                                                                       | 340                                                                                       |  |

| Number of independent analyzers                                    | 2, can be set up in state or timing modes                                                 | 2, can be set up in state or timing modes                                                 |  |

| Minimum master to master clock time* [1]                           | 5.988 ns                                                                                  | 5 ns                                                                                      |  |

| Minimum master to slave clock time                                 | 2 ns                                                                                      | 2 ns                                                                                      |  |

| Minimum slave to master clock time                                 | 2 ns                                                                                      | 2 ns                                                                                      |  |

| Minimum slave to slave clock time                                  | 5.988 ns                                                                                  | 5 ns                                                                                      |  |

| Setup/hold time* [1]<br>(single-clock, single-edge)                | 2.5 ns window adjustable from 4.5/-2.0 ns to -2.0/4.5 ns in 100 ps increments per channel | 2.5 ns window adjustable from 4.5/-2.0 ns to -2.0/4.5 ns in 100 ps increments per channel |  |

| Setup/hold time* [1]<br>(multi-clock, multi-edge)                  | 3.0 ns window adjustable from 5.0/-2.0 ns to -1.5/4.5 ns in 100 ps increments per channel | 3.0 ns window adjustable from 5.0/-2.0 ns to -1.5/4.5 ns in 100 ps increments per channel |  |

| Setup/hold time (on individual channels, after running eye finder) | 1.25 ns window                                                                            | 1.25 ns window                                                                            |  |

| Minimum state clock pulse width                                    | 1.2 ns                                                                                    | 1.2 ns                                                                                    |  |

| Time tag resolution [2]                                            | 4 ns                                                                                      | 4 ns                                                                                      |  |

| Maximum time count between states                                  | 17 seconds                                                                                | 17 seconds                                                                                |  |

| Maximum state tag count between states [2]                         | 232                                                                                       | 2 <sup>32</sup>                                                                           |  |

| Number of state clocks/qualifiers                                  | 4                                                                                         | 4                                                                                         |  |

| Maximum memory depth                                               | 16716A: 512K<br>16715A, 16717A: 2M                                                        | 16740A: 1M 16750B: 4M<br>16741A: 4M 16751B: 16M<br>16742A: 16M 16752B: 32M                |  |

| Maximum trigger sequence speed                                     | 167 MHz                                                                                   | 200 MHz                                                                                   |  |

| Maximum trigger sequence levels                                    | 16                                                                                        | 16                                                                                        |  |

<sup>\*</sup> All specifications noted by an asterisk are the performance standards against which the product is tested.

[1] Tested at input signal VH=-0.9V, VL=-1.7V, Slew rate=1V/ns, and threshold=-1.3V.

[2] Time or state tags halve the acquisition memory when there are no unassigned pods.

## Agilent Technologies 16715A, 16716A, 16717A, 16740A, 16741A, 16742A, 16750B, 16751B, 16752B Supplemental Specifications\* and Characteristics (continued)

| State Mode                        | 16715A, 16716A, 16717A<br>167 Mb/s State Mode                                                                                                                                                           | 16740A, 16741A, 16742A<br>16750B, 16751B, 16752B<br>200 Mb/s State Mode                                                                                                                                 |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trigger sequence level branching  | 4 way arbitrary "IF/THEN/ELSE" branching                                                                                                                                                                | 4 way arbitrary "IF/THEN/ELSE" branching                                                                                                                                                                |

| Trigger position                  | Start, center, end, or user defined                                                                                                                                                                     | Start, center, end, or user defined                                                                                                                                                                     |

| Trigger resources                 | 16 Patterns evaluated as =, ≠, >, <, ≥, ≤ 15 Ranges evaluated as in range, not in range (2 Timers per module) -1 2 Global counters 1 Occurrence counter per sequence level 4 Flags                      | 16 Patterns evaluated as =, ≠, >, <, ≥, ≤ 15 Ranges evaluated as in range, not in range (2 Timers per module) -1 2 Global counters 1 Occurrence counter per sequence level 4 Flags                      |

| Trigger resource conditions       | Arbitrary Boolean combinations                                                                                                                                                                          | Arbitrary Boolean combinations                                                                                                                                                                          |

| Trigger actions                   | Goto Trigger and fill memory Trigger and goto Store/don't store sample Turn on/off default storing Timer start/stop/pause/resume Global counter increment/reset Occurrence counter reset Flag set/clear | Goto Trigger and fill memory Trigger and goto Store/don't store sample Turn on/off default storing Timer start/stop/pause/resume Global counter increment/reset Occurrence counter reset Flag set/clear |

| Store qualification               | Default and per sequence level                                                                                                                                                                          | Default and per sequence level                                                                                                                                                                          |

| Maximum global counter            | 16,777,215                                                                                                                                                                                              | 16,777,215                                                                                                                                                                                              |

| Maximum occurrence counter        | 16,777,215                                                                                                                                                                                              | 16,777,215                                                                                                                                                                                              |

| Maximum pattern/range width       | 32 bits                                                                                                                                                                                                 | 32 bits                                                                                                                                                                                                 |

| Timers value range                | 100 ns to 5497 seconds                                                                                                                                                                                  | 100 ns to 5497 seconds                                                                                                                                                                                  |

| Timer resolution                  | 5 ns                                                                                                                                                                                                    | 5 ns                                                                                                                                                                                                    |

| Timer accuracy                    | 10 ns + .01%                                                                                                                                                                                            | 10 ns + .01%                                                                                                                                                                                            |

| Timer reset latency               | 70 ns                                                                                                                                                                                                   | 70 ns                                                                                                                                                                                                   |

| Data in to trigger out (BNC port) | 150 ns, typical                                                                                                                                                                                         | 150 ns, typical                                                                                                                                                                                         |

| Flag set/reset to evaluation      | 110 ns, typical                                                                                                                                                                                         | 110 ns, typical                                                                                                                                                                                         |

<sup>\*</sup> All specifications noted by an asterisk are the performance standards against which the product is tested.

#### Agilent Technologies 16715A, 16716A, 16717A, 16740A, 16741A, 16742A, 16750B, 16751B, 16752B Supplemental Specifications\* and Characteristics (continued)

| State Mode                                                        | 16717A<br>333 Mb/s State Mode                                                             | 16750B, 16751B, 16752B<br>400 Mb/s State Mode                                             |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Maximum state acquisition rate on each channel                    | 333 Mb/s                                                                                  | 400 Mb/s                                                                                  |

| Channel count                                                     | (Number of modules x 68) - 34                                                             | (Number of modules x 68) - 34                                                             |

| Maximum channels on a single time base and trigger                | 306                                                                                       | 306                                                                                       |

| Number of independent analyzers                                   | 1, when 333 MHz state mode is selected the second analyzer is turned off                  | 1, when 400 MHz state mode is selected the second analyzer is turned off                  |

| Minimum master to master clock time* [1]                          | 3.003 ns                                                                                  | 2.5 ns                                                                                    |

| Setup/hold time* [1]<br>(single-clock, single-edge)               | 2.5 ns window adjustable from 4.5/-2.0 ns to -2.0/4.5 ns in 100 ps increments per channel | 2.5 ns window adjustable from 4.5/-2.0 ns to -2.0/4.5 ns in 100 ps increments per channel |

| Setup/hold time* [1]<br>(single-clock, multi-edge)                | 3.0 ns window adjustable from 5.0/-2.0 ns to -1.5/4.5 ns in 100 ps increments per channel | 3.0 ns window adjustable from 5.0/-2.0 ns to -1.5/4.5 ns in 100 ps increments per channel |

| Setup/hold time (on individual channels after running eye finder) | 1.25 ns window                                                                            | 1.25 ns window                                                                            |

| Minimum state clock pulse width                                   | 1.2 ns                                                                                    | 1.2 ns                                                                                    |

| Time tag resolution [2]                                           | 4 ns                                                                                      | 4 ns                                                                                      |

| Maximum time count between states                                 | 17 seconds                                                                                | 17 seconds                                                                                |

| Number of state clocks                                            | 1                                                                                         | 1                                                                                         |

| Maximum memory depth                                              | 16717A: 2M                                                                                | 16750B: 4M<br>16751B: 16M<br>16752B: 32M                                                  |

| Maximum trigger sequence speed                                    | 333 MHz                                                                                   | 400 MHz                                                                                   |

| Maximum trigger sequence levels                                   | 15                                                                                        | 15                                                                                        |

| Trigger sequence level branching                                  | Dedicated next state branch or reset                                                      | Dedicated next state branch or reset                                                      |

| Trigger position                                                  | Start, center, end, or user defined                                                       | Start, center, end, or user defined                                                       |

<sup>\*</sup> All specifications noted by an asterisk are the performance standards against which the product is tested. [1] Tested at input signal VH=-0.9V, VL=-1.7V, Slew rate=1V/ns, and threshold=-1.3V.

<sup>[2]</sup> Time or state tags halve the acquisition memory when there are no unassigned pods.

## Agilent Technologies 16715A, 16716A, 16717A, 16740A, 16741A, 16742A, 16750B, 16751B, 16752B Supplemental Specifications\* and Characteristics (continued)

| State Mode                                         | 16717A<br>333 Mb/s State Mode                                                                                       | 16750B, 16751B, 16752B<br>400 Mb/s State Mode                                                                       |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Trigger resources                                  | 8 Patterns evaluated as =, ≠, >, <, ≥, ≤ 4 Ranges evaluated as in range, not in range 2 Occurrence counters 4 Flags | 8 Patterns evaluated as =, ≠, >, <, ≥, ≤ 4 Ranges evaluated as in range, not in range 2 Occurrence counters 4 Flags |

| Trigger resource conditions                        | Arbitrary Boolean combinations                                                                                      | Arbitrary Boolean combinations                                                                                      |

| Trigger actions                                    | Goto<br>Trigger and fill memory                                                                                     | Goto<br>Trigger and fill memory                                                                                     |

| Store qualification                                | Default                                                                                                             | Default                                                                                                             |

| Maximum occurrence counter                         | 16,777,215                                                                                                          | 16,777,215                                                                                                          |

| Maximum pattern/range width                        | 32 bits                                                                                                             | 32 bits                                                                                                             |

| Data in to trigger out (BNC port)                  | 150 ns, typical                                                                                                     | 150 ns, typical                                                                                                     |

| Flag set/reset to evaluation                       | 110 ns, typical                                                                                                     | 110 ns, typical                                                                                                     |

| Timing Mode                                        | 16715A, 16716A, 16717A                                                                                              | 16740A, 16741A, 16742A, 16750B, 16751B, 16752B                                                                      |

| Timing analysis sample rate (half/full channel)    | 667/333 MHz                                                                                                         | 800/400 MHz                                                                                                         |

| Channel count                                      | 68 per module                                                                                                       | 68 per module                                                                                                       |

| Maximum channels on a single time base and trigger | 340                                                                                                                 | 340                                                                                                                 |

| Number of independent analyzers                    | 2, can be setup in state or timing modes                                                                            | 2, can be setup in state or timing modes                                                                            |

| Sample period (full channel)                       | 3 ns to 1 ms                                                                                                        | 2.5 ns to 1 ms                                                                                                      |

| Sample period (half channel)                       | 1.5 ns                                                                                                              | 1.25 ns                                                                                                             |

| Minimum data pulse width for data capture          |                                                                                                                     |                                                                                                                     |

| Conventional timing                                | 1.75 ns                                                                                                             | 1.5 ns                                                                                                              |

| Transitional timing                                | 3.9 ns                                                                                                              | 3.8 ns                                                                                                              |

| For trigger sequencing                             | 6.1 ns                                                                                                              | 5.1 ns                                                                                                              |

| Sample period accuracy                             | ±(100 ps + .01% of sample period)                                                                                   | ±(100 ps + .01% of sample period)                                                                                   |

| Channel-to-channel skew                            | < 1.5 ns                                                                                                            | < 1.5 ns                                                                                                            |

| Time interval accuracy                             | ± (sample period + channel-to-channel skew + .01% of time interval reading)                                         | ± (sample period + channel-to-channel<br>skew + .01% of time interval reading)                                      |

| Minimum detectable glitch                          | 1.5 ns                                                                                                              | 1.5 ns                                                                                                              |

| Memory depth (half/full channel)                   | 16716A: 1M/512K<br>16715A, 16717A: 4/2M                                                                             | 16750B: 8/4M<br>16751B: 32/16M<br>16752B: 64/32M                                                                    |

<sup>\*</sup> All specifications noted by an asterisk are the performance standards against which the product is tested.

## Agilent Technologies 16715A, 16716A, 16717A, 16740A, 16741A, 16742A, 16750B, 16751B, 16752B Supplemental Specifications\* and Characteristics (continued)

| Timing Mode (continued)           | 16715A, 16716A, 16717A                                                                                                                             | 16740A, 16741A, 16742A<br>16750B, 16751B, 16752B                                                                                                   |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Maximum trigger sequence speed    | 167 MHz                                                                                                                                            | 200 MHz                                                                                                                                            |

| Maximum trigger sequence levels   | 16                                                                                                                                                 | 16                                                                                                                                                 |

| Trigger sequence level branching  | 4 way arbitrary "IF/THEN/ELSE" branching                                                                                                           | 4 way arbitrary "IF/THEN/ELSE" branching                                                                                                           |

| Trigger position                  | Start, center, end, or user defined                                                                                                                | Start, center, end, or user defined                                                                                                                |

| Trigger resources                 | 16 Patterns evaluated as =, ≠, >, <, ≥, ≤ 15 Ranges evaluated as in range, not in range 2 Edge/glitch (2 Timers per module) -1 2 Global counters   | 16 Patterns evaluated as =, ≠, >, <, ≥, ≤ 15 Ranges evaluated as in range, not in range 2 Edge/glitch (2 Timers per module) -1 2 Global counters   |

|                                   | 1 Occurrence counter per sequence level<br>4 Flags                                                                                                 | 1 Occurrence counter per sequence level<br>4 Flags                                                                                                 |

| Trigger resource conditions       | Arbitrary Boolean combinations                                                                                                                     | Arbitrary Boolean combinations                                                                                                                     |

| Trigger actions                   | Goto Trigger and fill memory Trigger and goto Timer start/stop/pause/resume Global counter increment/reset Occurrence counter reset Flag set/clear | Goto Trigger and fill memory Trigger and goto Timer start/stop/pause/resume Global counter increment/reset Occurrence counter reset Flag set/clear |

| Maximum global counter            | 16,777,215                                                                                                                                         | 16,777,215                                                                                                                                         |

| Maximum occurrence counter        | 16,777,215                                                                                                                                         | 16,777,215                                                                                                                                         |

| Maximum pattern/range width       | 32 bits                                                                                                                                            | 32 bits                                                                                                                                            |

| Timer value range                 | 100 ns to 5497 seconds                                                                                                                             | 100 ns to 5497 seconds                                                                                                                             |

| Timer resolution                  | 5 ns                                                                                                                                               | 5 ns                                                                                                                                               |

| Timer accuracy                    | ±10 ns + .01%                                                                                                                                      | ±10 ns + .01%                                                                                                                                      |

| Greater than duration             | 6 ns to 100 ms in 6 ns increments                                                                                                                  | 6 ns to 100 ms in 6 ns increments                                                                                                                  |

| Less than duration                | 12 ns to 100 ms in 6 ns increments                                                                                                                 | 12 ns to 100 ms in 6 ns increments                                                                                                                 |

| Timer reset latency               | 70 ns                                                                                                                                              | 70 ns                                                                                                                                              |

| Data in to trigger out (BNC port) | 150 ns, typical                                                                                                                                    | 150 ns, typical                                                                                                                                    |

| Flag set/reset to evaluation      | 110 ns, typical                                                                                                                                    | 110 ns, typical                                                                                                                                    |

<sup>\*</sup> All specifications noted by an asterisk are the performance standards against which the product is tested.

#### Probes for 16753A, 16754A, 16755A, 16756A, 16760A Supplemental Specifications\* and Characteristics

| Probes                                   | E5378A 100-pin Single-ended                            | E5379A 100-pin Differential                                                                                      | E5380A 35-pin Single-ended     | E5382A Single-Ended Flying Leads |

|------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------|

| Input resistance and capacitance         | Refer to figure 6.11                                   | Refer to figure 6.11                                                                                             | Refer to figure 6.11           | Refer to figure 6.12             |

| Maximum state data rate supported        | 1.5 Gb/s                                               | 1.5 Gb/s                                                                                                         | 600 Mb/s                       | 1.5 Gb/s                         |

| Mating connector                         | Agilent part number<br>1253-3620 [1]                   | Agilent part number<br>1253-3620 [1]                                                                             | Amp Mictor 38 [2]              | None required                    |

| Minimum voltage swing                    | 250 mV p-p                                             | $V_{in}^+$ - $V_{in}^-$ >= 200 mV p-p                                                                            | 300 mV p-p                     | 250 mV p-p                       |

| Input dynamic range                      | -3 Vdc to +5 Vdc                                       | -3 Vdc to +5 Vdc                                                                                                 | -3 Vdc to +5 Vdc               | -3 Vdc to +5 Vdc                 |

| Threshold accuracy                       | +/- (30 mV + 1% of setting)*                           | +/- (30 mV + 1% of setting) [3]                                                                                  | +/- (30 mV + 1% of setting)    | +/- (30 mV + 1% of setting)      |

| Threshold range                          | -3.0 V to +5.0 V                                       | -3.0 V to +5.0 V                                                                                                 | -3.0 V to +5.0 V               | -3.0 V to +5.0 V                 |

| User-supplied threshold input range      | -3.0 V to +5.0 V                                       | N/A                                                                                                              | N/A                            | N/A                              |

| User-supplied threshold input resistance | >= 100K ohms                                           | N/A                                                                                                              | N/A                            | N/A                              |

| Threshold control options                | User-provided input     Adjustable from user interface | If operated single-ended<br>(minus inputs grounded),<br>the threshold can be adjusted<br>from the user interface | Adjustable from user interface | Adjustable from user interface   |

| Maximum nondestructive input voltage     | +/-40 Vdc                                              | +/-40 Vdc                                                                                                        | +/-40 Vdc                      | +/-40 Vdc                        |

| Maximum input slew rate                  | 5 V/ns                                                 | 5 V/ns                                                                                                           | 5 V/ns                         | 5 V/ns                           |

| Clock input                              | Differential                                           | Differential                                                                                                     | Single-ended                   | Differential                     |

| Number of inputs [4]                     | 34 (32 data and 2 clock/data)                          | 17 (16 data and 1 clock/data)                                                                                    | 34 (32 data and 2 clock/data)  | 17 (16 data and 1 clock/data)    |

|                                          |                                                        |                                                                                                                  |                                |                                  |

All specifications noted by an asterisk are the performance standards against which the product is tested.

<sup>[5]</sup> Soft touch probes use a retention module attached to the target PC board. A kit of 5 retention modules is included with each probe. Additional kits of 5 retention modules can be ordered using Agilent part number E5387-68701.

| Model Number   | C <sub>1</sub> | R <sub>1</sub> | R <sub>2</sub> |

|----------------|----------------|----------------|----------------|

| E5378A, E5379A | 1.5pF          | 120            | 30             |

| E5380A         | 3pF            | 120            | 60             |

Figure 6.12. E5382A input equivalent probe load, with 5cm damped wire (see user's guide for load models with other accessories).

Figure 6.11. E5378A, E5379A, E5380A input equivalent probe load.

<sup>[1]</sup> A support shroud, Agilent part number 16760-02302 (for boards up to 0.062" thick) or 16760-02303 (for boards up to 0.120" thick) is recommended.

A kit of 5 shrouds and 5 connectors is available as Agilent part number 16760-68702 (for boards up to 0.062" thick) or 16760-68703 (for boards up to 0.120" thick).

<sup>[2]</sup> A kit of 5 Amp Mictor connectors and 5 support shrouds is available, Agilent part number E5346-68701.

A support shroud is available separately, Agilent part number £5364-44701.

[3] If operated single-ended (minus inputs grounded), the threshold can be adjusted from the user interface.

<sup>[4]</sup> Refer to specifications on specific modes of operation for details on how inputs can be used.

#### Probes for 16753A, 16754A, 16755A, 16756A, 16760A Supplemental Specifications\* and Characteristics (continued)

| E5387A Differential Soft Touch                                                                                   | E5390A Single-Ended Soft Touch                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Refer to figure 6.13                                                                                             | Refer to figure 6.13                                                                                                                                                                                                                                                                         |

| 1.5 Gb/s                                                                                                         | 1.5 Gb/s                                                                                                                                                                                                                                                                                     |

| None required [5]                                                                                                | None required [5]                                                                                                                                                                                                                                                                            |

| $V_{in}^{+} - V_{in}^{-} >= 200 \text{ mV p-p}$                                                                  | 250 mV p-p                                                                                                                                                                                                                                                                                   |

| -3 Vdc to +5 Vdc                                                                                                 | -3 Vdc to +5 Vdc                                                                                                                                                                                                                                                                             |

| +/- (30 mV + 2% of setting)*                                                                                     | +/- (30 mV + 2% of setting) [3]                                                                                                                                                                                                                                                              |

| -3.0 V to +5.0 V                                                                                                 | -3.0 V to +5.0 V                                                                                                                                                                                                                                                                             |

| N/A                                                                                                              | -3.0 V to +5.0 V                                                                                                                                                                                                                                                                             |

| N/A                                                                                                              | >= 100K ohms                                                                                                                                                                                                                                                                                 |

| If operated single-ended<br>(minus inputs grounded),<br>the threshold can be adjusted<br>from the user interface | User-provided input     Adjustable from user interface                                                                                                                                                                                                                                       |

| +/-40 Vdc                                                                                                        | +/-40 Vdc                                                                                                                                                                                                                                                                                    |

| 5 V/ns                                                                                                           | 5 V/ns                                                                                                                                                                                                                                                                                       |

| Differential                                                                                                     | Differential                                                                                                                                                                                                                                                                                 |

| 17 (16 data and 1 clock/data)                                                                                    | 34 (32 data and 2 clock/data)                                                                                                                                                                                                                                                                |

|                                                                                                                  | Refer to figure 6.13  1.5 Gb/s  None required [5]  Vin + Vin >= 200 mV p-p -3 Vdc to +5 Vdc +/- (30 mV + 2% of setting)* -3.0 V to +5.0 V  N/A  N/A  If operated single-ended (minus inputs grounded), the threshold can be adjusted from the user interface +/-40 Vdc  5 V/ns  Differential |

<sup>[5]</sup> Soft touch probes use a retention module attached to the target PC board. A kit of 5 retention modules is included with each probe. Additional kits of 5 retention modules can be ordered using Agilent part number E5387-68701.

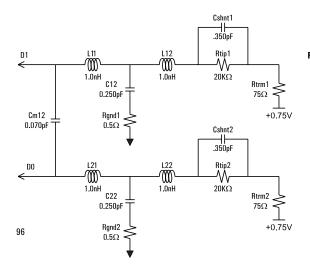

Figure 6.13. E5387A and E5390A Probe Load Model.

<sup>\*</sup> All specifications noted by an asterisk are the performance standards against which the product is tested.

[1] A support shroud, Agilent part number 16760-02302 (for boards up to 0.062" thick) or 16760-02303 (for boards up to 0.120" thick) is recommended. A kit of 5 shrouds and 5 connectors is available as Agilent part number 16760-68702 (for boards up to 0.062" thick) or 16760-68703 (for boards up to 0.120" thick).

<sup>[2]</sup> A kit of 5 Amp Mictor connectors and 5 support shrouds is available, Agilent part number E5346-68701. A support shroud is available separately, Agilent part number E5346-44701.

<sup>[3]</sup> If operated single-ended (minus inputs grounded), the threshold can be adjusted from the user interface.

<sup>[4]</sup> Refer to specifications on specific modes of operation for details on how inputs can be used.

#### Agilent 16753A, 16754A, 16755A, 16756A Supplemental Specifications\* and Characteristics

#### **Timing Zoom**

| Timing analysis sample rate               | 4 GHz                                         |  |

|-------------------------------------------|-----------------------------------------------|--|

| Time interval accuracy, within a pod pair | +/- (750 ps + 0.01% of time interval reading) |  |

| Time interval accuracy, between pod pairs | +/- (1.5 ns + 0.01% of time interval reading) |  |

| Memory depth                              | 64 K samples                                  |  |

| Trigger position                          | Start, center, end, or user defined           |  |

| Minimum data pulse width                  | 750 ps                                        |  |

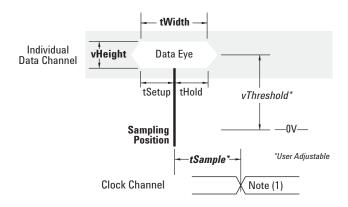

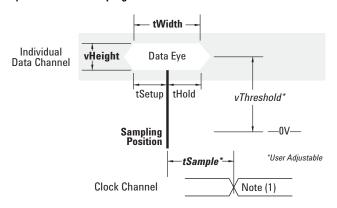

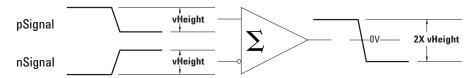

Figure 6.14. Data Sampling.

| State (synchronous) analysis mode                          | 300 Mb/s State Mode   | 600 Mb/s State Mode   |

|------------------------------------------------------------|-----------------------|-----------------------|

| tWidth*[1,2] with E5378A, E5379A, E5387A, or E5390A probes | 1 ns*, 600 ps typical | 1 ns*, 600 ps typical |

| tWidth[1] with E5380A or E5382A probes                     | 1.5 ns, 1 ns typical  | 1.5 ns, 1 ns typical  |

| tSetup                                                     | 0.5 tWidth            | 0.5 tWidth            |

| tHold                                                      | 0.5 tWidth            | 0.5 tWidth            |

| tSample range [3]                                          | -4 ns to +4 ns        | -4 ns to +4 ns        |

| tSample adjustment resolution                              | 80 ps (typical)       | 80 ps (typical)       |

| tSample accuracy, manual adjustment                        | +/- 300 ps            | +/- 300 ps [4]        |

<sup>[1]</sup> Minimum eye width in system under test

<sup>[2]</sup> The choice of probe can limit system performance. Select a probe rated at 600 Mb/s or greater to maintain system bandwidth.

<sup>[3]</sup> Sample positions are independently adjustable for each data channel input. A negative sample position causes the input to be synchronously sampled by that amount before each active clock edge. A positive sample position causes the input to be synchronously sampled by that amount after each active clock edge. A sampling position of zero causes the input to be synchronously sampled coincident with each clock edge.

<sup>[4]</sup> Use of eye finder is recommended in 600 Mb/s mode

Items marked with an asterisk \* are specifications. All others are characteristics.