## **16720A Pattern Generator Characteristics** Maximum memory depth 16 MVectors Number of output channels at $\leq$ 300 MHz clock 24 Number of output channels at $\leq$ 180 MHz clock 48 Number of output channels at $\leq$ 200 MHz clock 24 Number of output channels at $\leq$ 100 MHz clock 48 Number of different macros 100 Maximum number of lines in a macro 1024 Maximum number of parameters in a macro 10 Maximum number of macro invocations 1000 20000 Maximum loop count in a repeat loop 1000 Maximum number of repeat loop invocations Maximum number of "Wait" event patterns 4 3 Number of input lines to define a pattern 5 Maximum number of modules in a system Maximum width of a vector (in a 5 module system) 240 bits Maximum width of a label 32 bits Maximum number of labels 126 Maximum number of vectors in binary format 16 MVectors Minimum number of vectors in binary format 4096 Lead Set Characteristics

| Agilent 10474A 8-channel<br>probe lead set | Provides most cost effective lead set for the 16522A and<br>16720A clock and data pods. Grabbers are not included.<br>Lead wire length is 12 inches. |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Agilent 10347A 8-channel<br>probe lead set | Provides 50 $\Omega$ coaxial lead set for unterminated signals, required for 10465A ECL Data Pod (unterminated). Grabbers are not included.          |

| Agilent 10498A 8-channel<br>probe lead set | Provides most cost effective lead set for the 16522A and 16720A clock and data pods. Grabbers are not included. Lead wire length is 6 inches.        |

# **Data Pod Characteristics**

Note: Data Pod output parametrics depend on the output driver and the impedance load of the target system. Check the device data book for the specific drivers listed for each pod.

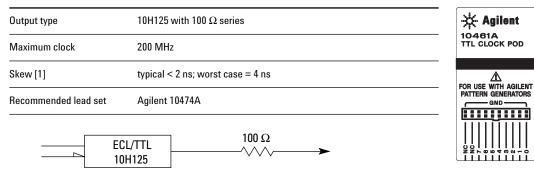

#### Agilent 10461A TTL Data Pod

## Agilent 10462A 3-State TTL/CMOS Data Pod

| Output type          | 74ACT11244 with 100 $\Omega$ series; 10H125 on non 3-state channel 7 [2] | -<br>🔆 Agilent                            |

|----------------------|--------------------------------------------------------------------------|-------------------------------------------|

| 3-state enable       | negative true, 100 K $\Omega$ to GND, enabled on no connect              | - 10462A<br>3-STATE TTL/<br>CMOS DATA POD |

| Maximum clock        | 100 MHz                                                                  |                                           |

| Skew [1]             | typical < 4 ns; worst case = 12 ns                                       |                                           |

| Recommended lead set | Agilent 10474A                                                           |                                           |

| 74A                  | CT11244 100 Ω                                                            |                                           |

#### Agilent 10464A ECL Data Pod (terminated)

| Output type          | 10H115 with 330 $\Omega$ pulldown, 47 $\Omega$ series | 🔆 Agilen                            |

|----------------------|-------------------------------------------------------|-------------------------------------|

| Maximum clock        | 300 MHz                                               | 10464A<br>ECL DATA PO<br>(TERMINATE |

| Skew [1]             | typical < 1 ns; worst case = 2 ns                     |                                     |

| Recommended lead set | Agilent 10474A                                        | PATTERN GENERA                      |

| 10                   | H115<br>348 Ω<br>-5.2 V                               | 227.004.00                          |

### Agilent 10465A ECL Data Pod (unterminated)

| Output type          | 10H115 (no termination)           | -🄆 Agilent                                 |

|----------------------|-----------------------------------|--------------------------------------------|

| Maximum clock        | 300 MHz                           | 10465A<br>ECL DATA POD<br>(UNTERMINATED)   |

| Skew [1]             | typical < 1 ns; worst case = 2 ns | A                                          |

| Recommended lead set | Agilent 10347A                    | FOR USE WITH AGILENT<br>PATTERN GENERATORS |

|                      | 1115                              |                                            |

#### Agilent 10466A 3-State TTL/3.3 volt Data Pod

| Output type          | 74LVT244 with 100 $\Omega$ series; 10H125 on non 3-state channel 7 [2] | -<br>- 🔆 Agilent                               |

|----------------------|------------------------------------------------------------------------|------------------------------------------------|

| 3-state enable       | negative true, 100 K $\Omega$ to GND, enabled on no connect            | - 10466A<br>3-STATE TTL /<br>3.3V DATA POD     |

| Maximum clock        | 200 MHz                                                                | - A FOR USE WITH AGILENT                       |

| Skew [1]             | typical < 3 ns; worst case = 7 ns                                      |                                                |

| Recommended lead set | Agilent 10474A                                                         | - <b>↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓</b> |

|                      | 100 Ω                                                                  | 80-F0004004-0                                  |

- 74LVT244

- [1] Typical skew measurements made at pod connector with approximately 10 pF/50 K  $\!\Omega$  load to GND; worst case skew numbers are a calculation of worst case conditions through circuits. Both numbers apply to any channel within a single or multiple module system. [2] Channel 7 on the 3-state pods has been brought out in parallel as a non 3-state signal. By looping this output back

- into the 3-state enable line, the channel can be used as a 3-state enable.

### Agilent 10469A 5 volt PECL Data Pod

#### Agilent 10471A 3.3 volt LVPECL Data Pod

| Output type          | 100LVEL90 (3.3V) with 215 ohm pulldown to ground and 42 ohm in series | Agilent                                  |

|----------------------|-----------------------------------------------------------------------|------------------------------------------|

| Maximum clock        | 300 MHz                                                               |                                          |

| Skew [1]             | typical < 500 ps; worst case = 1 ns                                   | FOR USE WITH AGILEM<br>PATTERN GENERATOR |

| Recommended lead set | Agilent 10498A                                                        |                                          |

|                      |                                                                       | —   <u> </u>                             |

#### Agilent 10473A 3-State 2.5 Volt Data Pod

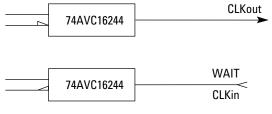

74AVC16244

| Output type          | 74AVC16244                                                 |                                                                                             |

|----------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 3-state enable       | negative true, 38 K $\Omega$ to GND, enabled on no connect | 10473A<br>3-STATE<br>2.5 V DATA POD                                                         |

| Maximum clock        | 300 MHz                                                    | <u> </u>                                                                                    |

| Skew [1]             | typical < 1.5 ns; worst case = 2 ns                        | FOR USE WITH AGILENT<br>PATTERN GENERATORS                                                  |

| Recommended lead set | Agilent 10498A                                             |                                                                                             |

|                      |                                                            | ₩<br>₩<br>₩<br>₩<br>₩<br>₩<br>₩<br>₩<br>₩<br>₩<br>₩<br>₩<br>₩<br>₩<br>₩<br>₩<br>₩<br>₩<br>₩ |

[2] Channel 7 on the 3-state pods has been brought out in parallel as a non 3-state signal. By looping this output back into the 3-state enable line, the channel can be used as a 3-state enable.

### Agilent 10476A 3-State 1.8 Volt Data Pod

| Output type          | 74AVC16244                                                 | -🄆 Agilent                                |

|----------------------|------------------------------------------------------------|-------------------------------------------|

| 3-state enable       | negative true, 38 K $\Omega$ to GND, enabled on no connect | 10476A<br>3-STATE<br>1.8 V DATA POD       |

| Maximum clock        | 300 MHz                                                    |                                           |

| Skew [1]             | typical < 1.5 ns; worst case = 2 ns                        | PATTERN GENERATORS                        |

| Recommended lead set | Agilent 10498A                                             |                                           |

| 74/                  | AVC16244                                                   | % ► 0 0 4 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |

#### Agilent 10483A 3-State 3.3 Volt Data Pod

| Output type          | 74AVC16244                                                 | -X- Agilent                         |

|----------------------|------------------------------------------------------------|-------------------------------------|

| 3-state enable       | negative true, 38 K $\Omega$ to GND, enabled on no connect | 10483A<br>3-STATE<br>3.3 V DATA POD |

| Maximum clock        | 300 MHz                                                    |                                     |

| Skew [1]             | typical < 1.5 ns; worst case = 2 ns                        | PATTERN GENERATORS                  |

| Recommended lead set | Agilent 10498A                                             |                                     |

|                      |                                                            |                                     |

74AVC16244

#### Agilent E8141A LVDS Data Pod

| Output type           | 65LVDS389 (LVDS data lines)           |                                            |

|-----------------------|---------------------------------------|--------------------------------------------|

|                       | 10H125 (TTL non-3-state channel 7)    | E8141A<br>LVDS DATA POD                    |

| 3-state enable        | positive true TTL; no connect=enabled | Δ                                          |

| Maximum clock         | 300 MHz                               | FOR USE WITH AGILENT<br>PATTERN GENERATORS |

| Skew                  | typical < 1 ns; worst case = 2 ns     | Eliiiiiiii                                 |

| Recommended lead set: | E8142A                                |                                            |

| Recommended lead set  | Agilent 10498A                        |                                            |

within a single or multiple module system.

65LVDS389

10 KΩ

ENABLE

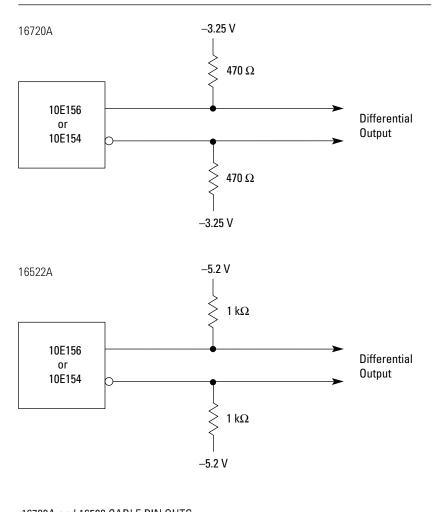

# **Data Cable Characteristics Without a Data Pod**

The Agilent 16720A and 16522A data cables without a data pod provide an ECL terminated (1 K $\Omega$  to -5.2V) differential signal (from a type 10E156 or 10E154 driver). These are usable when received by a differential receiver, preferably with a 100  $\Omega$  termination across the lines. These signals should not be used single ended due to the slow fall time and shifted voltage threshold (they are not ECL compatible).

16720A and 16522 CABLE PIN OUTS Gnd Gnd 7 6 5 4 3 2 1 0 Data Cable (Pod End) Gnd Gnd WITE WAITS WAITS NE CLINN NE CLIKOUT NE Gnd Gnd WITE WAITS WAITS NE CLINN NE CLIKOUT NE Gnd Gnd WITE WAITS WAITS NE CLINN NE CLIKOUT NE Gnd Gnd WITE WAITS WAITS NE CLIKN NE CLIKOUT NE Gnd Gnd WITE WAITS WAITS NE CLIKN NE CLIKOUT NE Gnd Gnd WITE WAITS WAITS NE CLIKN NE CLIKOUT NE Gnd Gnd WITE WAITS WAITS NE CLIKN NE CLIKOUT NE

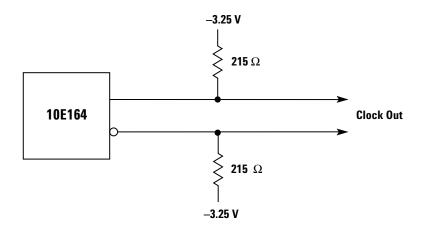

# **Clock Cable Characteristics Without a Clock Pod**

The Agilent 16720A and 16522A clock cables without a clock pod provide an ECL terminated (1 K $\Omega$  to –5.2V) differential signal (from a type 10E164 driver). These are usable when received by a differential receiver, preferably with a 100  $\Omega$  termination across the lines. These signals should not be used single ended due to the slow fall time and shifted voltage threshold (they are not ECL compatible).

# **Clock Pod Characteristics**

## 10460A TTL Clock Pod

| Clock output type         | 10H125 with 47 $\Omega$ series; true & inverted                                               |  |

|---------------------------|-----------------------------------------------------------------------------------------------|--|

| Clock output rate         | 100 MHz maximum                                                                               |  |

| Clock out delay           | approximately 8 ns total in 14 steps (16720A<br>only); 11 ns maximum in 9 steps (16522A only) |  |

| Clock input type          | TTL – 10H124                                                                                  |  |

| Clock input rate          | dc to 100 MHz                                                                                 |  |

| Pattern input type        | TTL – 10H124 (no connect is logic 1)                                                          |  |

| Clock-in to clock-out     | approximately 30 ns                                                                           |  |

| Pattern-in to recognition | approximately 15 ns + 1 clk period                                                            |  |

| Recommended lead set      | Agilent 10474A                                                                                |  |

|                           |                                                                                               |  |

| Agilent<br>10460A<br>TTL CLOCK POD         |

|--------------------------------------------|

| FOR USE WITH AGILENT<br>PATTERN GENERATORS |

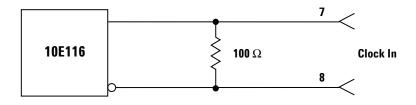

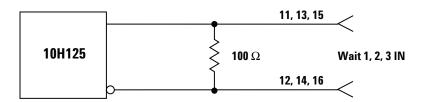

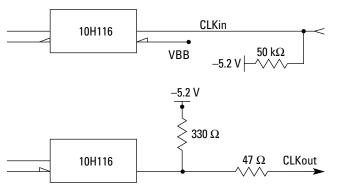

# 10463A ECL Clock Pod

| 10H116 differential unterminated; and differential unterminated; and differential with 330 $\Omega$ to –5.2V and 47 $\Omega$ series |  |

|-------------------------------------------------------------------------------------------------------------------------------------|--|

| 300 MHz maximum                                                                                                                     |  |

| approximately 8 ns total in 14 steps (16720A<br>only); 11 ns maximum in 9 steps (16522A only)                                       |  |

| ECL – 10H116 with 50 K $\Omega$ to –5.2v                                                                                            |  |

| dc to 300 MHz                                                                                                                       |  |

| ECL – 10H116 with 50 K $\Omega$ (no connect is logic 0)                                                                             |  |

| approximately 30 ns                                                                                                                 |  |

| approximately 15 ns + 1 clk period                                                                                                  |  |

| Agilent 10474A                                                                                                                      |  |

|                                                                                                                                     |  |

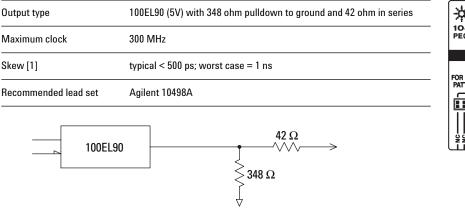

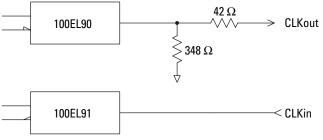

## 10468A 5 volt PECL Clock Pod

| Clock output type         | 100EL90 (5V) with 348 ohm pulldown to<br>ground and 42 ohm in series                          |  |

|---------------------------|-----------------------------------------------------------------------------------------------|--|

| Clock output rate         | 300 MHz maximum                                                                               |  |

| Clock out delay           | approximately 8 ns total in 14 steps (16720A<br>only); 11 ns maximum in 9 steps (16522A only) |  |

| Clock input type          | 100EL91 PECL (5V), no termination                                                             |  |

| Clock input rate          | dc to 300 MHz                                                                                 |  |

| Pattern input type        | 100EL91 PECL (5V), no termination (no connect is logic 0)                                     |  |

| Clock-in to clock-out     | approximately 30 ns                                                                           |  |

| Pattern-in to recognition | approximately 15 ns + 1 clk period                                                            |  |

| Recommended lead set      | Agilent 10498A                                                                                |  |

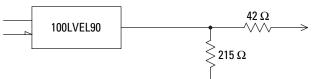

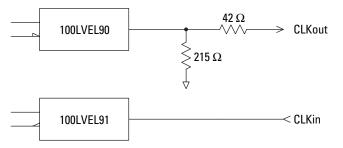

# 10470A 3.3 volt LVPECL Clock Pod

| Clock output type         | 100LVEL90 (3.3V) with 215 ohm pulldown to ground and 42 ohm in series                         |  |

|---------------------------|-----------------------------------------------------------------------------------------------|--|

| Clock output rate         | 300 MHz maximum                                                                               |  |

| Clock out delay           | approximately 8 ns total in 14 steps (16720A<br>only); 11 ns maximum in 9 steps (16522A only) |  |

| Clock input type          | 100LVEL91 LVPECL (3.3V), no termination                                                       |  |

| Clock input rate          | dc to 300 MHz                                                                                 |  |

| Pattern input type        | 100LVEL91 LVPECL (3.3V), no termination (no connect is logic 0)                               |  |

| Clock-in to clock-out     | approximately 30 ns                                                                           |  |

| Pattern-in to recognition | approximately 15 ns + 1 clk period                                                            |  |

| Recommended lead set      | Agilent 10498A                                                                                |  |

## 10472A 2.5 volt Clock Pod

| Clock output type         | 74AVC16244                                                                                    |

|---------------------------|-----------------------------------------------------------------------------------------------|

| Clock output rate         | 200 MHz maximum                                                                               |

| Clock out delay           | approximately 8 ns total in 14 steps (16720A<br>only); 11 ns maximum in 9 steps (16522A only) |

| Clock input type          | 74AVC16244 (3.6V max)                                                                         |

| Clock input rate          | dc to 200 MHz                                                                                 |

| Pattern input type        | 74AVC16244 (3.6V max; no connect is logic 0)                                                  |

| Clock-in to clock-out     | approximately 30 ns                                                                           |

| Pattern-in to recognition | approximately 15 ns + 1 clk period                                                            |

| Recommended lead set      | Agilent 10498A                                                                                |

|                           |                                                                                               |

## 10475A 1.8 volt Clock Pod

| 74AVC16244                                                                                    |  |

|-----------------------------------------------------------------------------------------------|--|

| 200 MHz maximum                                                                               |  |

| approximately 8 ns total in 14 steps (16720A<br>only); 11 ns maximum in 9 steps (16522A only) |  |

| 74AVC16244 (3.6V max)                                                                         |  |

| dc to 200 MHz                                                                                 |  |

| 74AVC16244 (3.6V max; no connect is logic 0)                                                  |  |

| approximately 30 ns                                                                           |  |

| approximately 15 ns + 1 clk period                                                            |  |

| Agilent 10498A                                                                                |  |

|                                                                                               |  |

| Agilent<br>10475A<br>1.8 V CLOCK POD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FOR USE WITH AGLENT<br>PATTERN GENERATORS<br>GND<br>LINE<br>USE WITH AGLENT<br>AND<br>ADD<br>LINE<br>STORES<br>OF USE WITH AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLENT<br>AGLE |

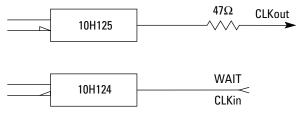

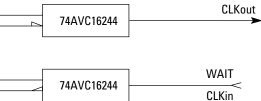

| 10477A 3.3 volt Clock Pod |                                                                                               | 🔆 Agilent                                  |               |

|---------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------|---------------|

| Clock output type         | 74AVC16244                                                                                    | 10477A<br>3.3 V CLOCK POD                  |               |

| Clock output rate         | 200 MHz maximum                                                                               |                                            |               |

| Clock out delay           | approximately 8 ns total in 14 steps (16720A<br>only); 11 ns maximum in 9 steps (16522A only) | FOR USE WITH AGLIENT<br>PATTERN GENERATORS |               |

| Clock input type          | 74AVC16244 (3.6V max)                                                                         |                                            |               |

| Clock input rate          | dc to 200 MHz                                                                                 |                                            |               |

| Pattern input type        | 74AVC16244 (3.6V max; no connect is logic 0)                                                  |                                            | CLKout        |

| Clock-in to clock-out     | approximately 30 ns                                                                           | 74AVC16244                                 |               |

| Pattern-in to recognition | approximately 15 ns + 1 clk period                                                            |                                            |               |

| Recommended lead set      | Agilent 10498A                                                                                | 74AVC16244                                 | WAIT<br>CLKin |

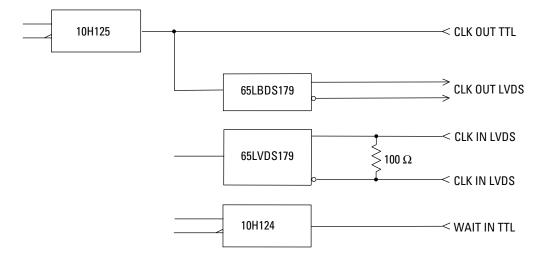

## E8140A LVDS Clock Pod

| Clock output type         | 65LVDS179 (LVDS) and 10H125 (TTL)    | 🔆 Agilent                                                                              |

|---------------------------|--------------------------------------|----------------------------------------------------------------------------------------|

| Clock output rate         | 200 MHz maximum (LVDS and TTL)       | E8140A<br>LVDS CLOCK POD                                                               |

| Clock out delay           | approximately 8 ns total in 14 steps | FOR USE WITH AGILENT                                                                   |

| Clock input type          | 65LVDS179 (LVDS with 100 ohm)        |                                                                                        |

| Clock input rate          | dc to 150 MHz (LVDS)                 | NC C C C C C C C C C C C C C C C C C C                                                 |

| Pattern input type        | 10H124 (TTL) (no connect = logic 1)  | CLK OU<br>CLK OU<br>CLK OU<br>CLK OU<br>CLK IN<br>CLK IN<br>CLK IN<br>WAIT 2<br>WAIT 0 |

| Clock-in to clock-out     | approximately 30 ns                  |                                                                                        |

| Pattern-in to recognition | approximately 15 ns + 1 clk period   |                                                                                        |

| Recommended lead set      | Agilent 10498A                       |                                                                                        |